# L99MM70XP

# Integrated microprocessor driven device intended for LIN controlled exterior mirrors

#### **Features**

- 5 V low-drop voltage regulator (150 mA max.)

- Embedded LIN transceiver: 2.0/2.1 compliant and SAEJ2602 compatible

- Independent control of mirror adjustment motors

- One full bridge for 3 A load ( $R_{on} = 300 \text{ m}\Omega$ )

- Two (three) half bridges for 0.5 A load  $(R_{on} = 1.6 \Omega)$

- One configurable high-side driver for up to 1.5 A load ( $R_{on} = 500 \text{ m}\Omega / 10 \text{ Watt bulb}$  control, or 1600 m $\Omega$  / LED control)

- Two high-side driver for 0.5 A load  $(R_{on} = 1600 \text{ m}\Omega)$

- One low-side driver 0.5 A load (R<sub>on</sub> = 1600 mΩ) used as half bridge with highside driver for independent mirror axis control

- One high-side driver for 6 A load  $(R_{on} = 90 \text{ m}\Omega)$

- One high-side driver for 0.5 A load (R<sub>on</sub> = 1600 mΩ) to supply an external MOSFET to drive an EC-glass

- Integrated EC glass control via an external MOSFET with fast discharge path: EC-glass can be discharged to GND or to -1 V

- Programmable soft start function to drive loads with higher inrush currents (>6 A, >1.5 A)

- Very low current consumption modes

- All outputs short-circuit and overtemperature protected

- Two thermal shutdown thresholds and early temperature warning

- Current monitor output for all high-side drivers

- Open-load diagnostic for all outputs

- Overload diagnostic for all outputs

- 3 PWM control signals for all outputs

- Charge pump output for active reverse polarity protection via an external N-channel MOSFET

- STM standard serial peripheral interface for control and diagnosis

- INH input for external CAN transceiver

### **Applications**

LIN controlled mirror

## **Description**

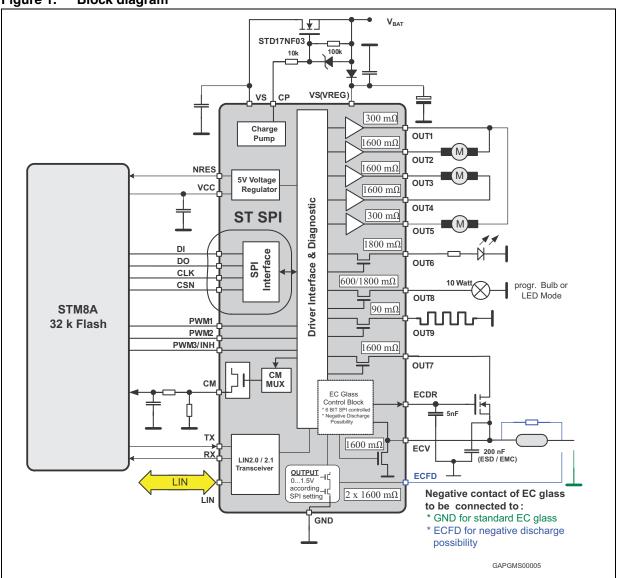

The L99MM70XP is a microcontroller driven multifunctional system ASSP dedicated for LIN controlled wing mirror applications. The device contains a voltage regulator to supply the microcontroller and a LIN2.1 physical layer. Up to 3 DC motors and five grounded resistive loads can independently be driven with four (five) half bridges and five high-side driver. The EC-glass control block provides overvoltage protection with a fast discharge path versus GND and a negative discharge path for future EC-glass characteristics. The integrated ST SPI controls all operation modes (forward, reverse, brake and high-impedance) and provides all the diagnostic information.

Table 1. Device summary

| Package     | Order codes |               |  |

|-------------|-------------|---------------|--|

| 1 ackage    | Tube        | Tape and reel |  |

| PowerSSO-36 | L99MM70XP   | L99MM70XPTR   |  |

September 2013 Doc ID 022637 Rev 2 1/68

Contents L99MM70XP

# **Contents**

| 1 | Bloc  | k diagram 8                                   |

|---|-------|-----------------------------------------------|

| 2 | Pin d | lefinitions and functions                     |

| 3 | Desc  | ription                                       |

|   | 3.1   | Voltage regulator 12                          |

|   | 3.2   | Power control in operating modes              |

|   |       | 3.2.1 Active mode                             |

|   |       | 3.2.2 Flash mode                              |

|   |       | 3.2.3 V <sub>CC-standby</sub> mode            |

|   |       | 3.2.4 V <sub>BAT-standby</sub> mode           |

|   | 3.3   | Wake-up events                                |

|   | 3.4   | Functional overview (truth table)15           |

|   | 3.5   | Interrupt 16                                  |

|   | 3.6   | Time-out watchdog                             |

|   | 3.7   | Passive mode                                  |

|   | 3.8   | Reset output (NRES)                           |

|   | 3.9   | V <sub>CC</sub> fail                          |

|   | 3.10  | Output drivers OUT1 OUT9 19                   |

|   |       | 3.10.1 Load condition                         |

|   |       | 3.10.2 Current monitor                        |

|   |       | 3.10.3 PWM inputs                             |

|   |       | 3.10.4 Cross current protection               |

|   |       | 3.10.5 Programmable soft start function       |

|   | 3.11  | Controller for electrochromic glass           |

|   | 3.12  | LIN bus interface                             |

|   |       | 3.12.1 General features                       |

|   |       | 3.12.2 LIN error handling                     |

|   |       | 3.12.3 Wake-up (from LIN bus)                 |

|   | 3.13  | Serial peripheral interface (ST SPI standard) |

| 4 | Prote | ection and diagnosis                          |

|   | 4.1   | Power supply fail                             |

|   |       |                                               |

|   |       | 4.1.1 Overvoltage                          |

|---|-------|--------------------------------------------|

|   |       | 4.1.2 Undervoltage                         |

|   | 4.2   | Diagnosis functions                        |

|   | 4.3   | Temperature warning and thermal shutdown   |

|   | 4.4   | Half bridge outputs                        |

|   | 4.5   | High-side driver outputs                   |

| 5 | Abso  | olute maximum ratings                      |

| 6 | ESD   | protection 31                              |

| 7 | Ther  | mal data                                   |

| 8 | Elect | rical characteristics                      |

|   | 8.1   | Supply and supply monitoring               |

|   | 8.2   | Oscillator 34                              |

|   | 8.3   | Power-on reset (V <sub>SREG</sub> )        |

|   | 8.4   | Voltage regulator V <sub>CC</sub>          |

|   | 8.5   | Reset output (V <sub>CC</sub> supervision) |

|   | 8.6   | Watchdog                                   |

|   | 8.7   | Current monitor output CM                  |

|   | 8.8   | Charge pump output CP                      |

|   | 8.9   | Outputs OUT1 – OUT9, ECV, ECFD             |

|   |       | 8.9.1 On-resistance                        |

|   |       | 8.9.2 Switching times                      |

|   |       | 8.9.3 Current monitoring                   |

|   |       | 8.9.4 Electrochrome control                |

|   |       | 8.9.5 INH/PWM3 input                       |

|   | 8.10  | LIN 43                                     |

|   | 8.11  | SPI and PWM inputs                         |

|   |       | 8.11.1 DC characteristics                  |

|   |       | 8.11.2 AC characteristics                  |

|   |       | 8.11.3 Dynamic characteristics             |

|   | 8.12  | Input PWM2 for Flash mode                  |

| 9 | SPI   | control and status registers5              |

|    | 9.1   | Functi   | onal description of the SPI | . 51 |

|----|-------|----------|-----------------------------|------|

|    |       | 9.1.1    | SPI communication flow      | 51   |

|    |       | 9.1.2    | Command byte                | 51   |

|    |       | 9.1.3    | Operation code definition   | 51   |

|    |       | 9.1.4    | Global status byte          | 52   |

|    |       | 9.1.5    | Address mapping             | 53   |

|    |       | 9.1.6    | Control registers           | 54   |

|    |       | 9.1.7    | Status registers            | 60   |

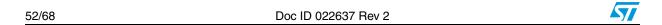

| 10 | Pack  | age an   | d packaging information     | . 65 |

|    | 10.1  | ECOP     | ACK®                        | . 65 |

|    | 10.2  | Power    | SSO-36 package information  | . 65 |

| 11 | Revis | sion his | etory                       | 67   |

L99MM70XP List of tables

# List of tables

| Table 1.  | Device summary                             | . 1 |

|-----------|--------------------------------------------|-----|

| Table 2.  | Pin definition and functions               | . 9 |

| Table 3.  | Wake-up events                             | 14  |

| Table 4.  | Functional overview (truth table)          | 15  |

| Table 5.  | Absolute maximum ratings                   | 30  |

| Table 6.  | ESD protection                             |     |

| Table 7.  | Operating junction temperature             | 32  |

| Table 8.  | Temperature warning and thermal shutdown   | 32  |

| Table 9.  | Supply and supply monitoring               | 33  |

| Table 10. | Oscillator                                 | 34  |

| Table 11. | Power-on reset (V <sub>SREG</sub> )        | 34  |

| Table 12. | Voltage regulator V <sub>CC</sub>          | 34  |

| Table 13. | Reset output (V <sub>CC</sub> supervision) | 35  |

| Table 14. | Watchdog                                   | 35  |

| Table 15. | Current monitor output CM                  | 36  |

| Table 16. | Charge pump output CP                      | 37  |

| Table 17. | On-resistance                              | 37  |

| Table 18. | Switching times                            | 38  |

| Table 19. | Current monitoring                         | 40  |

| Table 20. | Electrochrome control                      | 41  |

| Table 21. | INH/PWM3 input                             | 43  |

| Table 22. | LIN                                        | 43  |

| Table 23. | DC characteristics                         | 46  |

| Table 24. | AC characteristics                         | 47  |

| Table 25. | Dynamic characteristics                    | 47  |

| Table 26. | Input PWM2 for Flash mode                  |     |

| Table 27. | Command byte                               | 51  |

| Table 28. | Operation code definition                  | 51  |

| Table 29. | Global status byte                         | 52  |

| Table 30. | RAM memory map                             | 53  |

| Table 31. | ROM memory map                             |     |

| Table 32. | Control registers 1                        | 54  |

| Table 33. | Control registers 1, bits                  |     |

| Table 34. | Control registers 2                        |     |

| Table 35. | Control registers 2, bits                  |     |

| Table 36. | Control register 3                         |     |

| Table 37. | Control register 3, bits                   |     |

| Table 38. | Control register 4                         |     |

| Table 39. | Control register 4, bits                   | 57  |

| Table 40. | Configuration register                     |     |

| Table 41. | Configuration register, bits               |     |

| Table 42. | Status register 1                          |     |

| Table 43. | Status register 1, bits                    |     |

| Table 44. | Status register 2                          |     |

| Table 45. | Status register 2, bits                    |     |

| Table 46. | Status register 3                          |     |

| Table 47. | Status register 3, bits                    |     |

| Table 48. | Status register 4                          | 63  |

|           |                                            |     |

List of tables L99MM70XP

| Table 49. | Status register 4, bits     | 63 |

|-----------|-----------------------------|----|

|           | PowerSSO-36 mechanical data |    |

| Table 51. | Document revision history   | 67 |

L99MM70XP List of figures

# **List of figures**

| Figure 1.  | Block diagram                                                                     | 8  |

|------------|-----------------------------------------------------------------------------------|----|

| Figure 2.  | Pin connection (top view)                                                         |    |

| Figure 3.  | Voltage regulator operation                                                       | 13 |

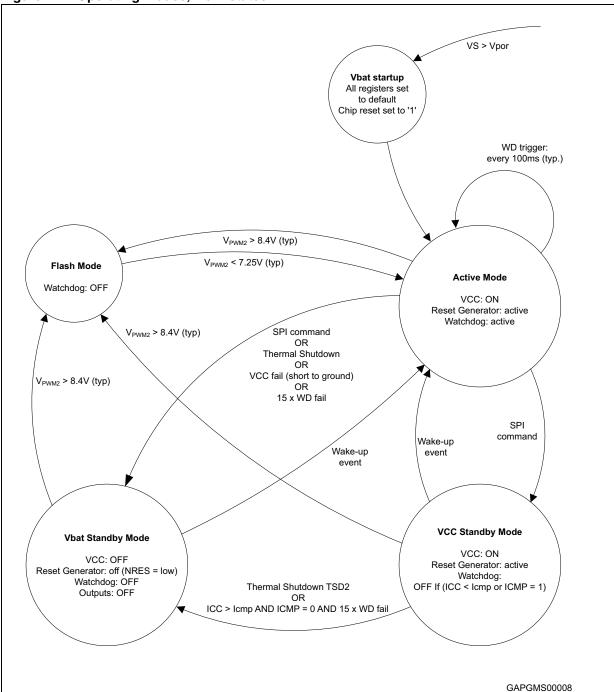

| Figure 4.  | Operating modes, main states                                                      | 16 |

| Figure 5.  | Watchdog state diagram                                                            | 18 |

| Figure 6.  | Example of programmable soft start function for inductive loads                   | 20 |

| Figure 7.  | SPI global error information output                                               | 24 |

| Figure 8.  | Thermal shutdown protection and diagnosis                                         | 28 |

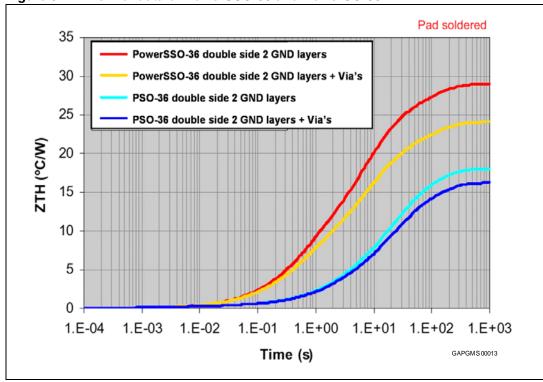

| Figure 9.  | Thermal data of PowerSSO-36 and PowerSO-36                                        | 32 |

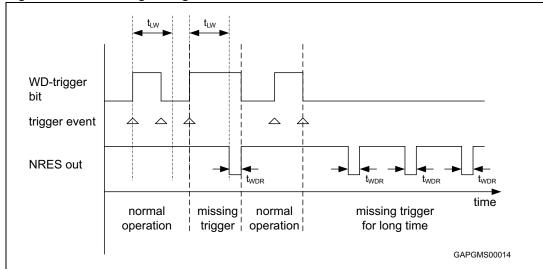

| Figure 10. | Watchdog timing                                                                   | 36 |

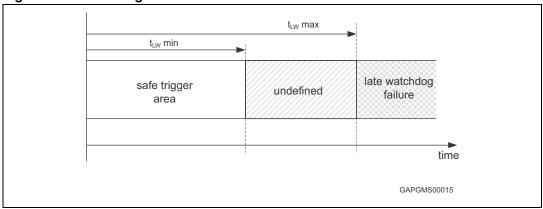

| Figure 11. | Watchdog late and safe window                                                     | 36 |

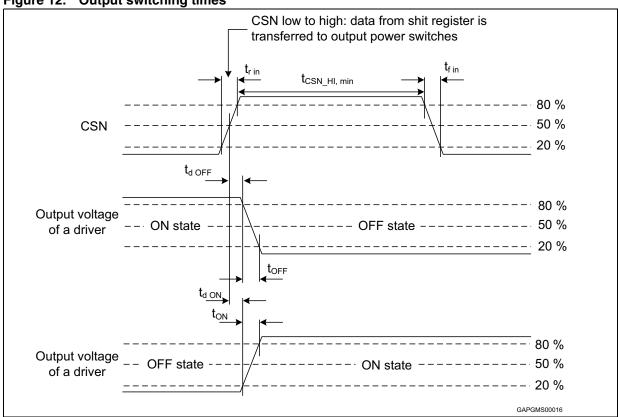

| Figure 12. | Output switching times                                                            | 39 |

| Figure 13. | Electrochrome mirror driver with mirror referenced to ground                      | 42 |

| Figure 14. | Electrochrome mirror driver with mirror referenced to ECFD for negative discharge | 42 |

| Figure 15. | LIN transmit and receive timing                                                   | 46 |

| Figure 16. | SPI timing parameters                                                             | 48 |

| Figure 17. | SPI input and output timing parameters                                            | 49 |

| Figure 18. | SPI maximum clock frequency                                                       | 49 |

| Figure 19  | PowerSSO-36 package dimensions                                                    | 65 |

Block diagram L99MM70XP

# 1 Block diagram

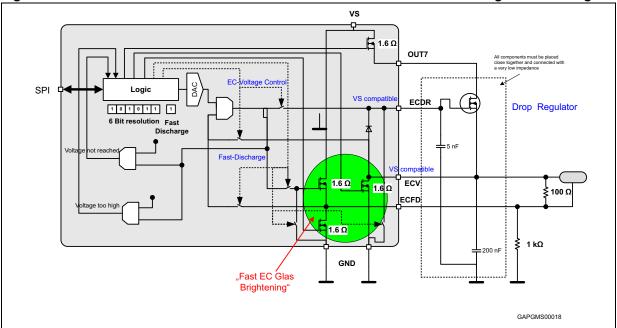

Figure 1. Block diagram

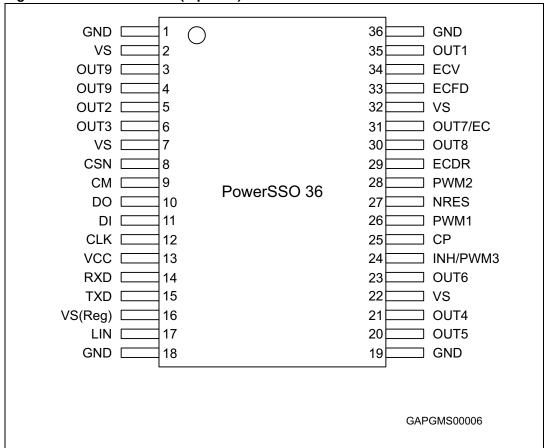

# 2 Pin definitions and functions

Table 2. Pin definition and functions

| Pin                    | Symbol                             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 18,<br>19, 36       | GND                                | Ground: reference potential Note: For the capability of driving the full current at the outputs all pins of GND must be externally connected!                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 2, 7, 32               | V <sub>S</sub> (Power1)            | Power supply voltage for outputs OUTX and ECFD (external reverse protection required): for this input a ceramic capacitor as close as possible to GND is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 22                     | V <sub>S</sub> (Power2)            | Note: For the capability of driving the full current at the outputs all pins of $V_S$ must be externally connected! Pins 2, 7 and 32 are internally connected, too. Pin 22 is the power supply for outputs OUT4, 5 and 6.                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 3, 4                   | OUT9                               | High-side driver output 9: the output is built by a high-side switch and is intended for resistive loads, hence the internal reverse diode from GND to the output is missing.For ESD reason a diode to GND is present but the energy which can be dissipated is limited. The high-side driver is a power DMOS transistor with an internal parasitic reverse diode from the output to V <sub>S</sub> (bulk-drain-diode). The output is overcurrent and open-load protected.  Note: For the capability of driving the full current at the outputs both pins of OUT9 must be externally connected! |  |  |

| 35, 5,<br>6, 21,<br>20 | OUT1, OUT2,<br>OUT3, OUT4,<br>OUT5 | Half bridge outputs 1,2,3,4,5: the output is built by a high-side and a low-side switch, which are internally connected. The output stage of both switches is a power DMOS transistor. Each driver has an internal parasitic reverse diode (bulk drain diode: high-side driver from output to $V_{\rm S}$ , low-side driver from GND to output). This output is overcurrent and openload protected.                                                                                                                                                                                             |  |  |

| 8                      | CSN                                | Chip select not input: this input is low active and requires CMOS logic levels. The serial data transfer between the L99MM70XP and the microcontroller is enabled by pulling the input CSN to low-level.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 9                      | СМ                                 | Current monitor output: depending on the selected multiplexer bits of the control register this output sources an image of the instant current through the corresponding high-side driver with a ratio of 1/10000 or 1/2000.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 10                     | DO                                 | Serial data output:<br>the diagnosis data is available via the SPI and this 3-state output. The output remains in<br>3-state, if the chip is not selected by the input CSN (CSN = high).                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 11                     | DI                                 | Serial data input:<br>the input requires CMOS logic levels and receives serial data from the microcontroller.<br>The data is a 24 bit control word and the most significant bit (MSB, bit 23) is transferred first.                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 12                     | CLK                                | Serial clock input: this input controls the internal shift register of the SPI and requires CMOS logic levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 13                     | VCC                                | Voltage regulator output: 5 V supply e.g. microcontroller, CAN transceiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 14                     | RXD                                | Receiver output of the LIN 2.1 transceiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 15                     | TXD                                | Transmitter input of the LIN 2.1 transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

Table 2. Pin definition and functions (continued)

| Pin | Symbol               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-----|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 16  | V <sub>S</sub> (Reg) | Power supply voltage (external reverse protection required): for this input a ceramic capacitor as close as possible to GND and an electrolytic capacitor to buffer the voltage during negative transients is recommended.                                                                                                                                                                                                                                         |  |  |

| 17  | LIN                  | LIN bus line                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 23  | OUT6                 | High-side driver output 6: The output is built by a high-side switch and is intended for resistive loads; hence the internal reverse diode from GND to the output is missing. For ESD reason a diode to GND is present but the energy which can be dissipated is limited. The high-side driver is a power DMOS transistor with an internal parasitic reverse diode from the output to $V_S$ (bulk-drain-diode). The output is overcurrent and open-load protected. |  |  |

| 24  | INH/PWM3             | Inhibit input: wake-up from external CAN transceiver. This pin has a second functionality. The microcontroller can use the INH signal to provide a third PWM input for the output OUT8.                                                                                                                                                                                                                                                                            |  |  |

| 25  | СР                   | Charge pump output: This output is provided to drive the gate of an external n-channel power MOS used for reverse polarity protection (see <i>Figure 1</i> ).                                                                                                                                                                                                                                                                                                      |  |  |

| 26  | PWM1                 | PWM1 input: This input signal can be used to control the drivers OUT1-OUT5, OUT7, and OUT9 by external PWM signal.                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 27  | NRES                 | Low active reset output to the microcontroller: internal pull up of typ. 100k $\Omega$                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 28  | PWM2                 | PWM2 input: This input signal can be used to control the driver OUT6 by an external PWM signal.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 29  | ECDR                 | ECDR: using the device in EC control mode this pin is used to control the gate of an external MOSFET.                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 30  | OUT8                 | High-side driver output 8: see OUT6  Note: This output can be configured to supply a bulb with low on-resistance or a LED with higher on-resistance in a different application.                                                                                                                                                                                                                                                                                    |  |  |

| 31  | OUT7/EC              | High-side driver output 7: see OUT6  Note: Beside the bit 8 in control register 2 this output can be switched on setting bit 0 for electrochrome control mode with higher priority.                                                                                                                                                                                                                                                                                |  |  |

| 33  | ECFD                 | ECFD: using the device in EC control mode this pin is used as "virtual GND" for the EC-glass. For EC-glasses, that require a negative discharge voltage, this supplies the fast discharge voltage. If no EC-glass is used, this pin must be connected to ground.                                                                                                                                                                                                   |  |  |

| 34  | ECV                  | ECV: Using the device in EC control mode this pin is used as voltage monitor input. For fast discharge an additional low-side-switch is implemented. This pin can be used as "stand alone" low-side as well. This output is intended for resistive loads only                                                                                                                                                                                                      |  |  |

# 3 Description

### 3.1 Voltage regulator

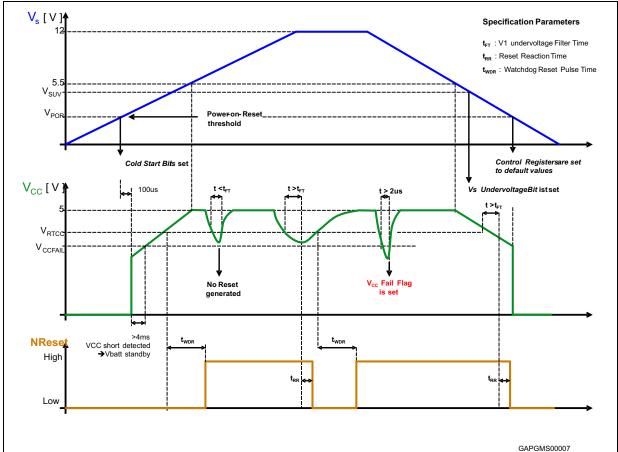

The L99MM70XP contains a fully protected low drop voltage regulator, which is designed for very fast transient response.

The output voltage is stable with load capacitors > 220 nF.

The voltage regulator provides 5 V supply voltage and up to 100 mA continuous load current for the external digital logic (microcontroller, etc...). In addition the regulator  $V_{CC}$  drives the L99MM70XP internal 5 V loads. The voltage regulator is protected against overload and overtemperature. An external reverse current protection has to be provided by the application circuitry to prevent the input capacitor from being discharged by negative transients or low input voltage. The output voltage precision is better than  $\pm 2$  % (incl. temperature drift and line-/load regulation) for operating mode; respectively  $\pm 3$  % during low current mode. Current limitation of the regulator ensures fast charge of external bypass capacitors. The output voltage is stable for ceramic load capacitors > 220 nF.

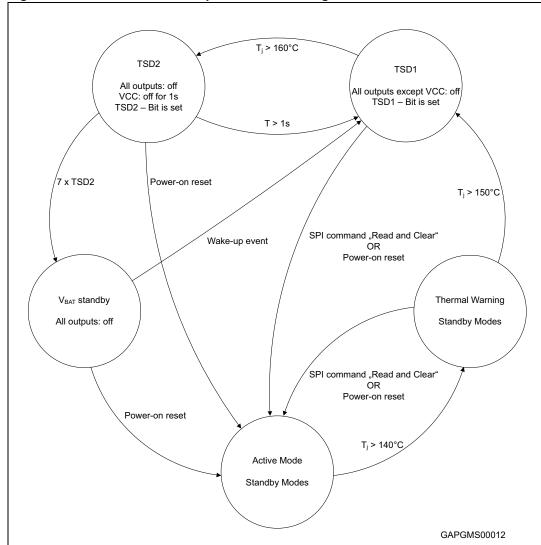

If device temperature exceeds TSD1 threshold, all outputs (OUTx, LIN) are deactivated except  $V_{CC}$ . Hence the microcontroller has the possibility for interaction or error logging. In case of exceeding TSD2 threshold (TSD2 > TSD1), also  $V_{CC}$  is deactivated (see *Figure 8*). A timer is started and the voltage regulator is deactivated for  $t_{TSD} = 1$  s.

During this time, all other wake-up sources (LIN) are disabled. After 1 s, the voltage regulator tries to restart automatically. If the restart fails 6 times without clearing and thermal shutdown condition still exists, the L99MM70XP enters the  $V_{BAT-standby}$  mode.

In case of short to GND at  $V_{CC}$  after initial turn on ( $V_{CC}$  < 2 V for at least 4 ms) the L99MM70XP enters the  $V_{BAT\text{-standby}}$  mode. Reactivation (wake-up) of the device can be achieved with signals from LIN or INH.

#### Figure 3. Voltage regulator operation

# 3.2 Power control in operating modes

The L99MM70XP can be operated in 4 different operating modes:

- Active

- Flash

- V<sub>CC-standby</sub>

- V<sub>BAT-standby</sub>

#### 3.2.1 Active mode

All functions are available. After at most 300 µs, the outputs can be enabled.

#### 3.2.2 Flash mode

To disable the watchdog feature a Flash program mode is available. The mode can be entered if the following condition occurs:

$V_{PWM2} \ge V_{Flash}$

Watchdog is disabled but all other functions are the same as in active mode.

Note: "High" level for flash mode selection is  $V_{PWM2} \ge V_{Flash}$ . For all other operation modes, standard 5 V logic signals are required.

### 3.2.3 V<sub>CC-standby</sub> mode

Outputs and internal loads are switched off. To supply the microcontroller in a low power mode, the voltage regulator ( $V_{CC}$ ) remains active. The intention of the  $V_{CC\text{-standby}}$  mode is to preserve the RAM contents.

A LIN wake-up event sets the device into the active mode and forces the RXD pin to the low-level.

A wake-up over INH switches device in active mode and start the watchdog.

The wake-up via SPI switches device in active mode. A status bit indicates the wake-up source

During the  $V_{CC\text{-standby}}$  mode, the current at  $V_{CC}$  is monitored.

The transition from active mode to V<sub>CC-standby</sub> mode is controlled by SPI.

### 3.2.4 V<sub>BAT-standby</sub> mode

To achieve minimum current consumption during  $V_{BAT\text{-standby}}$  mode, all L99MM70XP functions are switched off.

In  $V_{BAT-standbv}$  mode the current consumption of the L99MM70XP is reduced to 8  $\mu$ A.

The transition from active mode to V<sub>BAT-standby</sub> mode is controlled by SPI.

### 3.3 Wake-up events

A wake-up from standby mode switches the device to active mode. This can be initiated by one or more of the following sources:

- Change of the LIN state at LIN bus interfaces

- SPI access in V<sub>CC-standby</sub> mode (CSN is low and first rising edge on CLK)

- A current at the INH pin (I > 120  $\mu$ A) controlled by the CAN-transceiver (the CAN transceiver is not a part of the IC).

Table 3. Wake-up events

| Wake-up source                   | Description                                                                                                                                                                                                 |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIN                              | Always active                                                                                                                                                                                               |

| INH                              | Always active                                                                                                                                                                                               |

| V <sub>CC</sub> I <sub>CMP</sub> | Device remains in $V_{\text{CC-standby}}$ mode with watchdog enabled (If $I_{\text{CMP}} = 0$ ) and $V_{\text{CC}}$ goes into high current mode (increased current consumption). No interrupt is generated. |

| SPI access                       | Always active (except in V <sub>BAT-standby</sub> mode)                                                                                                                                                     |

LIN wake-up events in  $V_{\text{CC-standby}}$  mode generate a low-pulse at RXD for 56  $\mu s$ .

Wake-up from  $V_{\text{CC-standby}}$  by SPI access might be used to check the interrupt service handler.

# 3.4 Functional overview (truth table)

Table 4. Functional overview (truth table)

|                                    |                         | Operating modes |                                                      |                                         |  |

|------------------------------------|-------------------------|-----------------|------------------------------------------------------|-----------------------------------------|--|

| Function                           | Comments                | Active mode     | V <sub>CC-standby</sub><br>static mode               | V <sub>BAT-standby</sub><br>static mode |  |

| Voltage regulator, V <sub>CC</sub> | V <sub>OUT</sub> = 5 V  | On              | On <sup>(1)</sup>                                    | Off                                     |  |

| NRES                               |                         | On              | On                                                   | Off                                     |  |

| Window watchdog                    | V <sub>CC</sub> monitor | On              | Off (ON if $I_{CC} > I_{CMP}$<br>and $I_{CMP} = 0$ ) | Off                                     |  |

| LIN                                | LIN 2.1                 | On              | Off <sup>(2)</sup>                                   | Off <sup>(2)</sup>                      |  |

<sup>1.</sup> Supply the processor in low current mode.

<sup>2.</sup> The bus state is internally stored when going to standby mode. A change of bus state leads to a wake-up after exceeding of internal filter time.

# 3.5 Interrupt

In case of  $V_{CC\text{-standby}}$  mode and ( $I_{CC} > I_{CMPris}$ ), the device remains in standby mode, the  $V_{CC}$  regulator switches to high current mode and the watchdog is started. No interrupt is generated.

If bit NINTEN (CR1/Bit5, default value is set) is set, the RXD pin works also as interrupt output in case of wake-up by LIN or INH or SPI in  $V_{\text{CC-standby}}$  mode. This pin is pulled down for 56  $\mu$ s.

If it is not set, RXD is pulled down for 56us only for LIN wake-up.

### 3.6 Time-out watchdog

During normal operation, the watchdog monitors the microcontroller within a 100 ms trigger cycle.

In V<sub>BAT-standby</sub> and flash program modes, the watchdog circuit is automatically disabled.

After power on or standby mode, the watchdog is started immediately with the normal cycle time (100 ms). The microcontroller has to run its own setup and then to trigger the watchdog via the SPI. The trigger is finally accepted when the CSN input becomes high after the transmission of the SPI word.

Writing '1' to the watchdog trigger bit restarts the watchdog. Subsequently, the microcontroller has to serve the watchdog by alternating the watchdog trigger bit within the safe trigger area (refer to *Figure 10*). A correct watchdog trigger signal immediately starts the next cycle.

If the micro does not serve the watchdog in time, the watchdog pulls low the NRES output for 2 ms. At the same time, the watchdog failure counter (WDFAIL) is incremented by 1 and the device enters passive mode.

After 8 watchdog failures in sequence, the  $V_{CC}$  regulator is switched off for 200 ms. If subsequently, 7 additional watchdog failures occur, the  $V_{CC}$  regulator is completely turned off and the device goes into  $V_{BAT\text{-standby}}$  mode until a wake-up occurs.

In case of a watchdog failure, the outputs (OUTx) are switched off and the device enters passive mode (i.e. all control registers are set to default values).

Vbat standby mode (8+7)x WD failures Wake-up event VCC off for 200ms 200 ms 8x WD failure Watchdog failure (No trigger) Reset Invert trigger bit Watchdog active (NRES low for before end of 2ms) watchdog time After 2 ms Poweron Reset Wake-up event from VCC standby or flash mode Watchdog inactive: Vbat standby Wake-up event VCC standby from Vbat standby Flash mode Go to standby or flash mode GAPGMS00009

#### Figure 5. Watchdog state diagram

#### 3.7 Passive mode

L99MM70XP enters passive mode in case of:

- Watchdog failure

- V<sub>CC</sub> under voltage (NRES)

- Thermal shutdown TSD2

- SPI data in stuck at 0 or 1

In passive mode all control registers (except the reset level bit RSTLVL) and the configuration register are set to default so that all outputs are switched off. The PASSIVE bit inside the global status byte is set to "1". The first valid SPI frame after entering the passive mode resets the PASSIVE bit to "0" and leaves passive.

# 3.8 Reset output (NRES)

If  $V_{CC}$  is turned on and the voltage exceeds the  $V_{CC}$  reset threshold, the reset output NRES is pulled up by internal pull up resistor to  $V_{CC}$  voltage after a 2 ms reset delay time. This is necessary for a defined start of the microcontroller when the application is switched on.

A low active reset pulse (2 ms) is generated in case of:

- V<sub>CC</sub> drops below V<sub>rth</sub> (configurable by SPI) for more than 8 μs (V<sub>CC</sub> under voltage)

- Watchdog failure

If NRES is pulled low, all control registers (except the reset level bit RSTLVL) and the configuration register are set to default. In both cases, the device enters passive mode.

# 3.9 V<sub>CC</sub> fail

The V<sub>CC</sub> regulator output voltage is monitored.

In case of a drop below the  $V_{CC}$  fail threshold ( $V_{CC}$  < 2 V typ. for t > 2  $\mu$ s), the  $V_{CC}$  fail bit is latched. The fail bit is cleared by a dedicated SPI command.

If 4 ms after turn on of the regulator the  $V_{CC}$  voltage is below the  $V_{CC}$  fail threshold, the L99MM70XP identifies a short circuit condition at the regulator output and switch it off.

In case of V<sub>CC</sub> short to GND failure the device enters V<sub>BAT-standby</sub> mode automatically.

### 3.10 Output drivers OUT1 ... OUT9

#### 3.10.1 Load condition

Each half bridge is built by internally connected high-side and low-side power DMOS transistors. Due to the built-in reverse diodes of the output transistors, inductive loads can be driven at the outputs OUT1 to OUT5 without external free-wheeling diodes. The drivers OUT6, OUT7, OUT8, OUT9, ECV and ECFD are intended to drive resistive loads. Therefore only a limited energy (E < 1 mJ) can be dissipated by the internal ESD-diodes in freewheeling condition. For inductive loads (L > 100  $\mu$ H) an external free wheeling diode connected between GND and the corresponding output is required.

#### 3.10.2 Current monitor

The current monitor output sources a current image at the current monitor output, which has two fixed ratios of the instantaneous current of the selected high-side driver. Outputs with a resistance of 500 m $\Omega$  and higher have a ratio of 1/2000 and those with a lower resistance of 1/10000. The signal at output CM is blanked after switching on the driver until correct settlement of the circuitry (at least for 32  $\mu$ s). The bits 0 to 3 of the control register 3 define which of the outputs are multiplexed to the current monitor output CM. The current monitor output allows a more precise analysis of the actual state of the load rather than the detection of an open-load or overload condition. For example, it can be used to detect the motor state (starting, free running, stalled). Moreover, it is possible to control the power of the defroster more precisely by measuring the load current.

#### **3.10.3 PWM inputs**

Each driver has a corresponding PWM enable bit, which can be programmed by the SPI interface. If the PWM enable bit is set in control register 2 or 3, the output is controlled by the logically AND-combination of the PWM signal and the output control bit in control register 0 or 1. The outputs OUT1-5, 7, 9, ECV are controlled by the PWM1 input, the output OUT6 is controlled by the input PMW2 and output OUT8 is controlled by INH/PWM3. Thus, the three PWM inputs can be used to dim three lamps independently by external PWM signals.

Switching off the outputs, a delay of maximum 300  $\mu$ s is introduced (see also *Table 18* in *Section 8.9.2: Switching times*), hence the off time of the PWM input signal should be at least 300  $\mu$ s.

#### 3.10.4 Cross current protection

The half bridges of the device are cross current protected by an internal delay time. If one driver (LS or HS) is turned off, the activation of the other driver of the same half bridge is automatically delayed by the cross current protection time. After the cross current protection time is expired, the slew-rate limited switch off phase of the driver is changed to a fast turn-off phase and the opposite driver is turned on with slew-rate limitation. Due to this behavior, it is always guaranteed that the previously activated driver is completely turned off before the opposite driver starts to conduct.

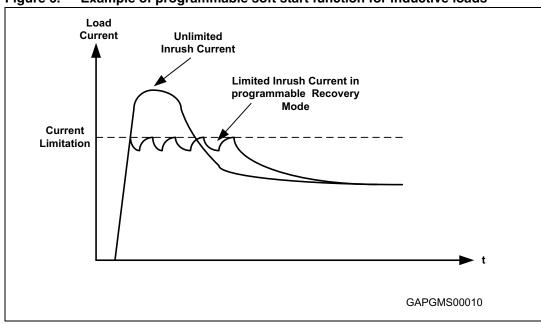

#### 3.10.5 Programmable soft start function

Loads with startup currents higher than the overcurrent limits (e.g. inrush current of lamps, start current of motors and cold resistance of heaters) can be driven by using the programmable soft start function (i.e. overcurrent recovery mode). Each driver has a corresponding overcurrent recovery bit. If this bit is set, the device automatically switches the outputs on again after a programmable recovery time. The duty cycle in overcurrent condition can be programmed by the SPI interface to about 12 % or 25 %. The PWM modulated current provides sufficient average current to power-up the load (e.g. heat up the bulb) until the load reaches operating condition. The PWM frequency settles at 1.7 kHz and 3 kHz.

The device itself cannot distinguish between a real overload and a non-linear load like a light bulb. A real overload condition can only be qualified by time. As an example, the microcontroller can switch on the light bulbs by setting the overcurrent recovery bit for the first 50 ms. After clearing the recovery bit, the output is automatically switched off, if the overload condition remains.

Figure 6. Example of programmable soft start function for inductive loads

### 3.11 Controller for electrochromic glass

The voltage of an electrochromic element connected at pin ECV can be controlled to a target value, which is set by the bits EC<5:0> (Control register 2, bits 6 down to 1). Setting bit ECON (control register 2, bit 0) enables this function. An on-chip differential amplifier and an external MOS source follower, with its gate connected to pin ECDR, and which drives the electrochrome mirror voltage at pin ECV, form the control loop. The drain of the external MOS transistor is supplied by OUT7. A diode from pin ECV (anode) to pin ECDR (cathode) has been placed on the chip to protect the external MOS source follower. A capacitor of at least 5 nF has to be added to pin ECDR for loop-stability. The target voltage is binary coded with a full-scale range of 1.5 V. If bit ECVL (control register 3, bit 5) is set to '1', the maximum controller output voltage is clamped to 1.2 V without changing the resolution of bits EC<5:0>. When programming the ECVLS driver to on-state, the voltage at pin ECV is pulled to ground by a 1.6 Ohm low-side switch until the voltage at pin ECV is less than dV<sub>ECVhi</sub> higher than the target voltage (fast discharge).

The status of the voltage control loop is reported via SPI. Bit ECVO (status register 3, bit 4) is set, if the voltage at pin ECV is higher, whereas bit ECVNR (status register 3, bit 5) is set, if the voltage at pin ECV is lower than the target value. Both status bits are valid, if the voltage is stable for at least the ECVO/ECVNR filter time and are not latched.

Since OUT7 is the output of a high-side driver, it contains the same diagnose functions as the other high-side drivers (e.g. during an overcurrent detection, the control loop is switched off). In electrochrome mode, OUT10 cannot be controlled by PWM mode. For EMS reasons the loop capacitor at pin ECDR as well as the capacitor between ECV and GND have to be placed to the respective pins as close as possible (see *Figure 13* for details).

If the electrochrome element is connected between the pins ECV and ECFD instead between ECV and ground, a negative voltage can be applied to the device by pulling ECFD to a higher value than ECV, which is connected to ground by a 1.6 Ohm low-side switch. In this mode the voltage at pin ECFD is controlled to the target value defined by the register EC<5:0>. This is done using an on-chip source-follower transistor (see *Figure 14* for details). The negative discharge is enabled by setting bit ECND (control register 2, bit 7) to '1'.

During normal (positive) voltage control the low-side driver at pin ECFD must be switched on to connect the electrochrome element to ground.

Pin ECDR is pulled resistively (R<sub>ECDRDIS</sub>) to ground while not in electrochrome mode.

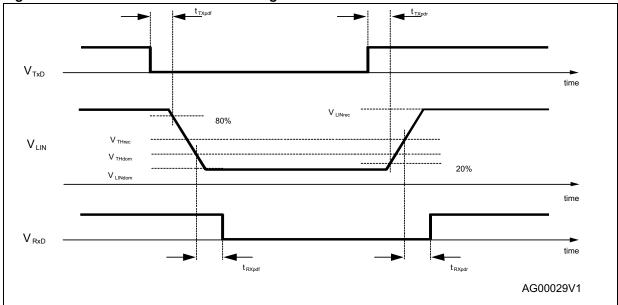

#### 3.12 LIN bus interface

#### 3.12.1 General features

- Speed communication up to 20 kbit/s

- High speed Flash mode 100 kbit/s

- LIN 2.1 compliant (SAEJ2602 compatible) transceiver

- Function range from +40 V to -18 V DC at LIN pin

- GND disconnection fail safe at module level

- Off mode: does not disturb network

- GND shift operation at system level

- Microcontroller Interface with CMOS compatible I/O pins

- Pull up internal resistor

- ESD: immunity against automotive transients per ISO7637 specification

- Matched output slopes and propagation delay

In order to further reduce the current consumption in standby mode, the integrated LIN bus interface offers an ultra low current consumption.

#### 3.12.2 LIN error handling

The L99MM70XP provides the following 3 error handling features which are not described in the LIN Specifications V2.1, but are realized in different stand alone LIN transceivers/microcontrollers to switch the application back to normal operation mode.

#### **Dominant TXD time out**

A permanent low-level on pin TXD would force the bus into a permanent dominant state, blocking all network communication. If pin TXD remains at low-level for longer than the TXD dominant timeout  $t_{dom(TXD)}$ , the transmitter is disabled. The status bit is latched and can be read and optionally cleared by SPI. The transmitter remains disabled until the status register is cleared. This feature can be disabled via SPI.

#### LIN BUS permanent recessive

If TXD changes to low-level but the bus does not follow within  $t_{rec(LIN)}$ , the transmitter is disabled. The status bit is latched and can be read and optionally cleared by SPI. The transmitter remains disabled until the status register is cleared.

#### LIN BUS permanent dominant

If a dominant state on the bus persists for longer than  $t_{dom(LIN)}$  a permanent dominant status is detected. The status bit is latched and can be read and optionally cleared by SPI. The transmitter of the transceiver is not disabled.

Note:

A wake-up caused by a message on the bus starts the voltage regulator and the microcontroller to switch the application back to normal operation mode.

#### 3.12.3 Wake-up (from LIN bus)

In standby mode the L99MM70XP can receive a wake-up from LIN bus. For the wake-up feature the L99MM70XP logic differentiates two different conditions.

#### Normal wake-up

Normal wake-up can occur when the L99MM70XP was set in standby mode while a recessive (state was present on the bus. A dominant level at LIN for  $t > t_{linbus}$ , switches the L99MM70XP to active mode. An interrupt is generated at the RXD/NINT pin.

#### Wake-up from short to GND condition

If the L99MM70XP was set in standby mode while LIN was in dominant (low) state, recessive level at LIN for  $t_{linbus}$ , switches the L99MM70XP to active mode. An interrupt is generated at the RXD/NINT pin.

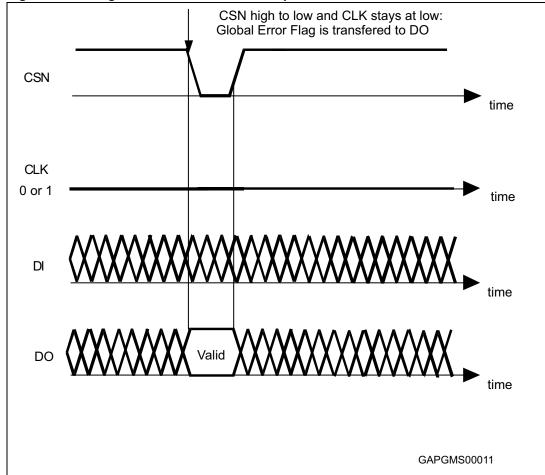

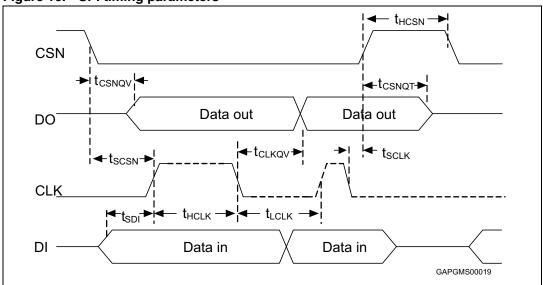

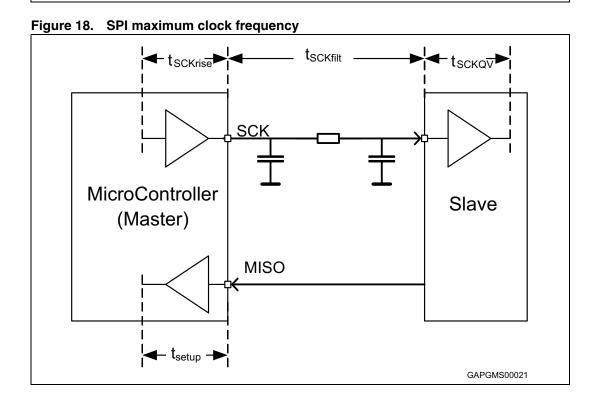

### 3.13 Serial peripheral interface (ST SPI standard)

A 24 bit ST-SPI is used for bi-directional communication with the microcontroller.

During active mode, the SPI

- Triggers the watchdog

- Controls the modes and status of all L99MM70XP modules (incl. input and output drivers)

- Provides driver output diagnostic

- Provides L99MM70XP diagnostic (incl. overtemperature warning, L99MM70XP operation status)

Note: During standby modes, the SPI is generally deactivated.

The SPI can be driven by a microcontroller with its SPI peripheral running in following mode:

CPOL = 0 and CPHA = 0.

For this mode, input data is sampled by the low to high transition of the clock CLK, and output data is changed from the high to low transition of CLK.

This device is not limited to microcontroller with a build-in SPI. Only three CMOS-compatible output pins and one input pin are needed to communicate with the device. A fault condition can be detected by setting CSN to low. If CSN = 0, the DO pin reflects the global error flag (fault condition) of the device (see *Figure 7*). This operation does not cause the communication error bit in the global status byte to be set.

Figure 7. SPI global error information output

#### **Chip Select Not (CSN)**

The input pin is used to select the serial interface of this device. When CSN is high, the output pin (DO) is in high impedance state. A low signal activates the output driver and a serial communication can be started. The state during CSN = 0 is called a communication frame.

#### Serial Data In (DI)

The input pin is used to transfer data serially into the device. The data applied to the DI are sampled at the rising edge of the CLK signal and shifted into an internal 24 bit shift register. At the rising edge of the CSN signal the contents of the shift register is transferred to data input register. The writing to the selected data input register is only enabled if exactly 24 bits are transmitted within one communication frame (i.e. CSN low). If more or less clock pulses are counted within one frame the complete frame is ignored. This safety function is implemented to avoid an activation of the output stages by a wrong communication frame.

Note:

Due to this safety functionality a daisy chaining of SPI is not possible. Instead, a parallel operation of the SPI bus by controlling the CSN signal of the connected IC's is recommended.

#### Serial Data Out (DO)

The data output driver is activated by a logical low-level at the CSN input and goes from high impedance to a low or high-level depending on the global error flag (fault condition). The first rising edge of the CLK input after a high to low transition of the CSN pin transfers the content of the selected status register into the data out shift register. Each subsequent falling edge of the CLK shifts out the next bit.

#### Serial Clock (CLK)

The CLK input is used to synchronize the input and output serial bit streams. The Data Input (DI) is sampled at the rising edge of the CLK and the Data Output (DO) changes with the falling edge of the CLK signal.

# 4 Protection and diagnosis

### 4.1 Power supply fail

Overvoltage and undervoltage detection on V<sub>S</sub> (Power1).

#### 4.1.1 Overvoltage

If the supply voltage  $V_S$  rises above the overvoltage threshold ( $V_{SOV}$ ) for more than 56  $\mu s$  (typ.)

- The outputs OUT1-9, ECV, ECFD and LIN are switched to high impedance state (load protection). Electrochrome mode is switched off. If the bit OVUVR is set to 0, the outputs are re-enabled automatically if the overvoltage condition is removed. If it is set to 1, then the overvoltage bit has to be cleared to re-enable the outputs. LIN is always automatically re-enabled.

- The overvoltage bit is set and can be cleared with a "read and clear" command.

#### 4.1.2 Undervoltage

If the supply voltage  $V_S$  drops below the under voltage threshold voltage ( $V_{SUV}$ ) for more than 56  $\mu s$  (typ.)

- The outputs OUT1-9, ECV, ECFD and LIN are switched to high impedance state. Electrochrome mode is switched off. If the bit OVUVR is set to 0, the outputs are reenabled automatically if the under voltage condition is removed. If it is set to 1, then the under voltage bit has to be cleared to re-enable the outputs. LIN is always automatically re-enabled.

- The under voltage bit is set and can be cleared with the "read and clear" command.

# 4.2 Diagnosis functions

Digital diagnosis features are provided by SPI:

- V<sub>CC</sub> reset (threshold programmable)

- Overtemperature including pre warning

- Open-load status separately for each output OUT1-9, ECV, ECFD

- Overload status separately for each output OUT1-9, ECV, ECFD

- V<sub>S-supply</sub> overvoltage undervoltage

- V<sub>CC</sub> fail bit

- Chip reset bit (start from power-on reset)

- Number of unsuccessful V<sub>CC</sub> restarts after thermal shutdown

- Number of sequential watchdog failures

- LIN diagnosis (permanent recessive/dominant, dominant TXD)

- Device state (wake-up from V<sub>CC-standby</sub> or V<sub>BAT-standby</sub>)

- Forced V<sub>BAT-standby</sub> after WD-fail, forced V<sub>BAT-standby</sub> after overtemperature

- Watchdog timer state (diagnosis of watchdog)

- Passive mode

- SPI communication error

Figure 8. Thermal shutdown protection and diagnosis

# 4.3 Temperature warning and thermal shutdown

See Figure 8.

# 4.4 Half bridge outputs

The device provides a total of 5 half bridge outputs OUT1,2,3,4,5 to drive inductive loads (e.g. motor).

The half bridges are protected against

- Overvoltage and undervoltage

- Overload (short circuit)

- Overtemperature with pre warning

If the output current exceeds the current shutdown threshold the output transistor is turned off and the corresponding diagnosis bit of the output is latched. The status can be read and cleared from SPI. If the overcurrent recovery mode is set for this output, the output is switched on again in order to provide a soft start function (see *Section 3.10.5: Programmable soft start function*) and the status bit is cleared automatically. Otherwise the output stays off until the status bit is cleared.

The outputs are automatically switched off in case of passive mode,  $V_S$  undervoltage,  $V_S$  overvoltage, thermal shutdown (TSD1 and TSD2) or stuck at 1/0 condition at DI.

### 4.5 High-side driver outputs

The device provides a total of 4 high-side outputs OUT6,7,8,9 to drive LED or defroster.

The high-side outputs are protected against

- Overvoltage and undervoltage (can be masked by SPI)

- Overload (short circuit)

- Overtemperature with pre warning

If the output current exceeds the current shutdown threshold the output transistor is turned off and the corresponding diagnosis bit of the output is latched. The status can be read and cleared from SPI. If the overcurrent recovery mode is set for this output, the output is switched on again in order to provide a soft start function (see *Section 3.10.5: Programmable soft start function*) and the status bit is cleared automatically. Otherwise the output stays off until the status bit is cleared.

The outputs are automatically switched off in case of passive mode,  $V_S$  undervoltage,  $V_S$  overvoltage, thermal shutdown (TSD1 and TSD2) or stuck at 1/0 condition at DI.

Note:

Loss of ground or ground shift with externally grounded loads: ESD structures are configured for nominal currents only. If external loads are connected to different grounds, the current load must be limited to this nominal current.

# 5 Absolute maximum ratings

Table 5. Absolute maximum ratings

| Symbol                                                                                                                                                                           | Parameter/test condition                                               | Value<br>[DC voltage]            | Unit                         |   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------|------------------------------|---|

| V <sub>S</sub>                                                                                                                                                                   | DC supply voltage/jump start                                           | -0.3 to +28                      | V                            |   |

|                                                                                                                                                                                  | Load dump                                                              |                                  | -0.3 to +40                  | ٧ |

| V                                                                                                                                                                                | Stabilized aupply voltage legic cupply                                 | V <sub>S</sub> < 5.2 V           | -0.3 to V <sub>S</sub> + 0.3 | V |

| V <sub>CC</sub>                                                                                                                                                                  | Stabilized supply voltage, logic supply                                | V <sub>S</sub> > 5.2 V           | -0.3 to 5.5                  | V |

| V <sub>DI</sub> , V <sub>CLK</sub> , V <sub>TXD</sub> ,<br>V <sub>CSN</sub> , V <sub>DO</sub> ,<br>V <sub>RXD</sub> , V <sub>NRES</sub> ,<br>V <sub>CM</sub> , V <sub>PWM1</sub> | Logic input/output voltage range                                       | Logic input/output voltage range |                              | V |

| V <sub>PWM2</sub> , V <sub>PWM3</sub>                                                                                                                                            | Logic input voltage                                                    |                                  | -0.3 to V <sub>S</sub> + 0.3 | ٧ |

| V <sub>CP</sub>                                                                                                                                                                  | Charge pump output                                                     |                                  | -25 to 39                    | V |

| V <sub>OUTn,ECDR,ECV,</sub><br>ECFD                                                                                                                                              | Static output voltage (n = 1 to 9)                                     |                                  | -0.3 to V <sub>S</sub> + 0.3 | V |

| I <sub>OUT2,3,4,6,7,ECV,</sub><br>ECFD <sup>,</sup> I <sub>V</sub> S(REG)                                                                                                        | Output current <sup>(1)</sup>                                          |                                  | ±1.25                        | Α |

| I <sub>OUT1,5,8,9</sub> ,<br>I <sub>VS(Power)</sub> ,I <sub>GND</sub>                                                                                                            | Output current <sup>(1)</sup>                                          |                                  | ±5                           | Α |

| I <sub>Pin to Pin</sub>                                                                                                                                                          | Maximum output current between pin 2 and 32 or 7 and 32 <sup>(1)</sup> |                                  | ±1                           | Α |

| V <sub>LIN</sub>                                                                                                                                                                 | LIN bus I/O voltage range                                              | -20 to +40                       | V                            |   |

Values for the absolute maximum current through bond wire. It doesn't consider maximum power dissipation or other limits.

Note:

All maximum ratings are absolute ratings. Exceeding the limitation of any of these values may cause an irreversible damage of the integrated circuit!

L99MM70XP ESD protection

# 6 ESD protection

Table 6. ESD protection

| Parameter                                             | Value             | Unit |

|-------------------------------------------------------|-------------------|------|

| All pins <sup>(1)</sup>                               | ±2                | kV   |

| All output pins <sup>(2)</sup> (OUT1-OUT9, ECV, ECFD) | ±4                | kV   |

| LIN <sup>(2)</sup>                                    | ±8 <sup>(3)</sup> | kV   |

| All pins (charge device model) <sup>(4)</sup>         | ±500              | V    |

| Corner pins (charge device model) <sup>(4)</sup>      | ±750              | V    |

<sup>1.</sup> HBM (human body model, 100 pF, 1.5 k $\Omega$ ) according to MIL 883C, Method 3015.7 or EIA/JESD22A114-A.

For detailed information please see EMC report from IBEE Zwickau (available on request).

<sup>2.</sup> HBM with all unzapped pins grounded.

<sup>3.</sup> With external components.

<sup>4.</sup> According charged device model: JEDEC JESD22-C101D.

Thermal data L99MM70XP

### 7 Thermal data

Table 7. Operating junction temperature

| Symbol | Parameter                      |            |    |

|--------|--------------------------------|------------|----|

| Tj     | Operating junction temperature | -40 to 150 | °C |

Note: R<sub>thjA</sub>, typical value, without PCB.

Table 8. Temperature warning and thermal shutdown

| Symbol               | Parameter                                 |                               | Min. | Тур. | Max. | Unit |

|----------------------|-------------------------------------------|-------------------------------|------|------|------|------|

| T <sub>W ON</sub>    | Thermal overtemperature warning threshold | T <sub>j</sub> <sup>(1)</sup> | 130  | 140  | 150  | °C   |

| T <sub>SD1 OFF</sub> | Thermal shutdown junction temperature 1   | T <sub>j</sub> <sup>(1)</sup> | 140  | 150  | 160  | °C   |

| T <sub>SD2 OFF</sub> | Thermal shutdown junction temperature 2   | T <sub>j</sub> <sup>(1)</sup> | 150  | 160  | 170  | °C   |

<sup>1.</sup> Non-overlapping.

Figure 9. Thermal data of PowerSSO-36 and PowerSO-36

### 8 Electrical characteristics

# 8.1 Supply and supply monitoring

The voltages are referred to ground and currents are assumed positive, when the current flows into the pin. 6 V  $\leq$  VS  $\leq$  18 V; all outputs open;  $T_{amb}$  = -40 °C...125 °C, unless otherwise specified.

Table 9. Supply and supply monitoring

| Symbol                          | Parameter                                                                           | Test condition                                                                                    | Min. | Тур. | Max. | Unit |

|---------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>SUV ON</sub>             | V <sub>S</sub> undervoltage threshold voltage                                       | V <sub>S</sub> increasing                                                                         | 5.7  |      | 7.2  | V    |

| V <sub>SUV OFF</sub>            | V <sub>S</sub> undervoltage threshold voltage                                       | V <sub>S</sub> decreasing                                                                         | 5.5  |      | 6.9  | V    |

| V <sub>SUV hyst</sub>           | V <sub>S</sub> undervoltage hysteresis                                              | V <sub>SUV ON</sub> - V <sub>SUV OFF</sub>                                                        |      | 0.5  |      | V    |

| V <sub>SOV OFF</sub>            | V <sub>S</sub> overvoltage threshold voltage                                        | V <sub>S</sub> increasing                                                                         | 18.1 |      | 24.5 | V    |

| V <sub>SOV ON</sub>             | V <sub>S</sub> overvoltage threshold voltage                                        | V <sub>S</sub> decreasing                                                                         | 17.5 |      | 23.5 | V    |

| V <sub>SOV hyst</sub>           | V <sub>S</sub> overvoltage hysteresis                                               | V <sub>SOV OFF</sub> - V <sub>SOV ON</sub>                                                        |      | 1    |      | V    |

| I <sub>VS(act)</sub>            | Current consumption in active mode                                                  | $V_S = 13.5 \text{ V, TXD LIN high}^{(1)(2)}$                                                     |      | 7    | 20   | mA   |

| I <sub>VSREG(act)</sub>         | Current consumption in active mode                                                  | $V_{SREG} = 13.5 \text{ V, TXD LIN high}$<br>$I_{VCC} = 0^{(2)}$                                  |      | 6    | 12   | mA   |

| I <sub>VS(BAT)</sub>            | Current consumption in V <sub>BAT-standby</sub> mode                                | $V_S = 13.5 V^{(1)(2)}$                                                                           |      | 1    |      | μA   |

| I <sub>VS(BAT)</sub>            | Current consumption in V <sub>BAT-standby</sub> mode                                | $V_S = 13.5 V^{(1)(3)}$                                                                           |      | 2    |      | μΑ   |

| I <sub>VSREG(BAT)</sub>         | Current consumption in V <sub>BAT-standby</sub> mode                                | V <sub>SREG</sub> = 13.5 V <sup>(2)</sup>                                                         | 1    | 8    | 16   | μΑ   |

| I <sub>VSREG(BAT)</sub>         | Current consumption in V <sub>BAT-standby</sub> mode                                | V <sub>SREG</sub> = 13.5 V <sup>(3)</sup>                                                         | 2    | 12   | 24   | μΑ   |

| I <sub>VS(VBAT)</sub><br>wupend | Current consumption in V <sub>BAT-standby</sub> mode with a pending wake-up request | V <sub>S</sub> , V <sub>SREG</sub> = 13.5 V,<br>2 V < LIN < V <sub>S</sub> - 3.5 V                |      | 800  | 1200 | μΑ   |

| I <sub>VS(VCC)</sub><br>wupend  | Current consumption in V <sub>CC-standby</sub> mode with a pending wake-up request  | V <sub>S</sub> , V <sub>SREG</sub> = 13.5 V,<br>2 V < LIN < V <sub>S</sub> - 3.5 V                |      | 800  | 1200 | μΑ   |

| I <sub>VS(VCC)</sub>            | Current consumption in V <sub>CC-standby</sub> mode                                 | $V_S$ = 13.5 V, voltage regulator $V_{CC}$ active, no wake-up request                             |      | 1    |      | μA   |

| I <sub>VSREG(VCC)</sub>         | Current consumption in V <sub>CC-standby</sub> mode                                 | $V_S = 13.5$ V, voltage regulator $V_{CC}$ active, no wake-up request, $I_{VCC} = 0^{(2)}$        | 10   | 45   | 70   | μΑ   |

| I <sub>VSREG(VCC)</sub>         | Current consumption in V <sub>CC-standby</sub> mode                                 | $V_S = 13.5 \text{ V, voltage regulator } V_{CC}$ active, no wake-up request, $I_{VCC} = 0^{(3)}$ | 15   | 67   | 105  | μΑ   |

<sup>1.</sup> OUT1 - OUT9, ECDR ECV, ECFD floating.

<sup>2.</sup>  $T_{Test} = -40 \,^{\circ}\text{C}$ , 25  $^{\circ}\text{C}$ .

<sup>3.</sup>  $T_{Test} = 85$  °C. This parameter is guaranteed by design.

Electrical characteristics L99MM70XP

#### 8.2 Oscillator

The voltages are referred to ground and currents are assumed positive, when the current flows into the pin. 4.5 V  $\leq$  V<sub>S</sub>  $\leq$  28 V; all outputs open;  $T_{amb}$  = -40 °C...125 °C, unless otherwise specified.

Table 10. Oscillator

| Symbol           | Parameter             | Test condition | Min. | Тур. | Max. | Unit |

|------------------|-----------------------|----------------|------|------|------|------|

| f <sub>CLK</sub> | Oscillation frequency |                | 1.6  | 2.0  | 2.70 | MHz  |

# 8.3 Power-on reset (V<sub>SREG</sub>)

All outputs open; T<sub>amb</sub> = -40 °C...125 °C, unless otherwise specified (see *Figure 3*).

Table 11. Power-on reset (V<sub>SREG</sub>)

| Symbol           | Parameter                  | Test condition               | Min. | Тур. | Max. | Unit |

|------------------|----------------------------|------------------------------|------|------|------|------|

| V                | V throohold                | V <sub>SREG</sub> increasing | 2.8  | 3.8  | 4.5  | V    |

| V <sub>POR</sub> | V <sub>POR</sub> threshold | V <sub>SREG</sub> decreasing |      | 3.2  |      | V    |

# 8.4 Voltage regulator V<sub>CC</sub>

The voltages are referred to ground and currents are assumed positive, when the current flows into the pin. 6 V  $\leq$  V<sub>SREG</sub>  $\leq$  28 V; T<sub>amb</sub> = -40 °C...125 °C, unless otherwise specified.

Table 12. Voltage regulator V<sub>CC</sub>

| Symbol              | Parameter                                                | Test condition                                                 | Min. | Тур. | Max. | Unit |

|---------------------|----------------------------------------------------------|----------------------------------------------------------------|------|------|------|------|

| V <sub>CC</sub>     | Output voltage                                           |                                                                |      | 5.0  |      | ٧    |

| V <sub>CC</sub>     | Output voltage tolerance active mode                     | I <sub>LOAD</sub> = 6 mA50 mA,<br>V <sub>SREG</sub> = 13.5 V   |      |      | ±2   | %    |

| V <sub>hc</sub>     | Output voltage tolerance active mode, high current       | I <sub>LOAD</sub> = 50 mA100 mA,<br>V <sub>SREG</sub> = 13.5 V |      |      | ±2.5 | %    |

| V <sub>STB</sub>    | Output voltage tolerance V <sub>CC-standby</sub> mode    | $I_{LOAD} = 0 \mu A6 mA,$<br>$V_{SREG} = 13.5 V$               | -2.5 |      | 3.5  | %    |

| V                   | Drop out voltage                                         | $I_{LOAD} = 50 \text{ mA}, V_{SREG} = 4.5 \text{ V}$           |      | 0.2  | 0.4  | ٧    |

| $V_{DP}$            | Drop-out voltage                                         | I <sub>LOAD</sub> = 100 mA, V <sub>SREG</sub> = 4.5 V          |      | 0.3  | 0.5  | ٧    |

| I <sub>CC</sub>     | Output current in active mode                            | Max. continuous load current                                   |      |      | 100  | mA   |

| I <sub>CCmax</sub>  | Short circuit output current                             | Current limitation                                             | 400  | 600  | 950  | mA   |

| Cload1              | Load capacitor1                                          | Ceramic                                                        | 0.22 |      |      | μF   |

| t <sub>TSD</sub>    | V <sub>CC</sub> deactivation time after thermal shutdown |                                                                |      | 1    |      | S    |

| I <sub>CMPris</sub> | Current consumption rising threshold                     | Rising current (deactivated current monitor)                   | 1.6  | 3.2  | 5.2  | mA   |

Table 12. Voltage regulator V<sub>CC</sub> (continued)

| Symbol              | Parameter                             | Test condition                                | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------------|-----------------------------------------------|------|------|------|------|

| I <sub>CMPfal</sub> | Current consumption falling threshold | Falling current (deactivated current monitor) | 1.3  | 2.7  |      | mA   |

| I <sub>CMPhys</sub> | Current consumption hysteresis        |                                               |      | 0.5  |      | mA   |

| V <sub>CCfail</sub> | V <sub>CC</sub> fail threshold        | V <sub>CC</sub> forced                        |      | 2    |      | V    |

# 8.5 Reset output (V<sub>CC</sub> supervision)

The voltages are referred to ground and currents are assumed positive, when the current flows into the pin. 4 V  $\leq$  V<sub>S</sub>  $\leq$  28 V;  $T_{amb}$  = -40 °C...125 °C, unless otherwise specified.

Table 13. Reset output (V<sub>CC</sub> supervision)

| Symbol               | Parameter                      | Test condition                                             | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------|------------------------------------------------------------|------|------|------|------|